英特尔14纳米工艺技术(en 免费下载)

- 2026-05-15 16:07:15

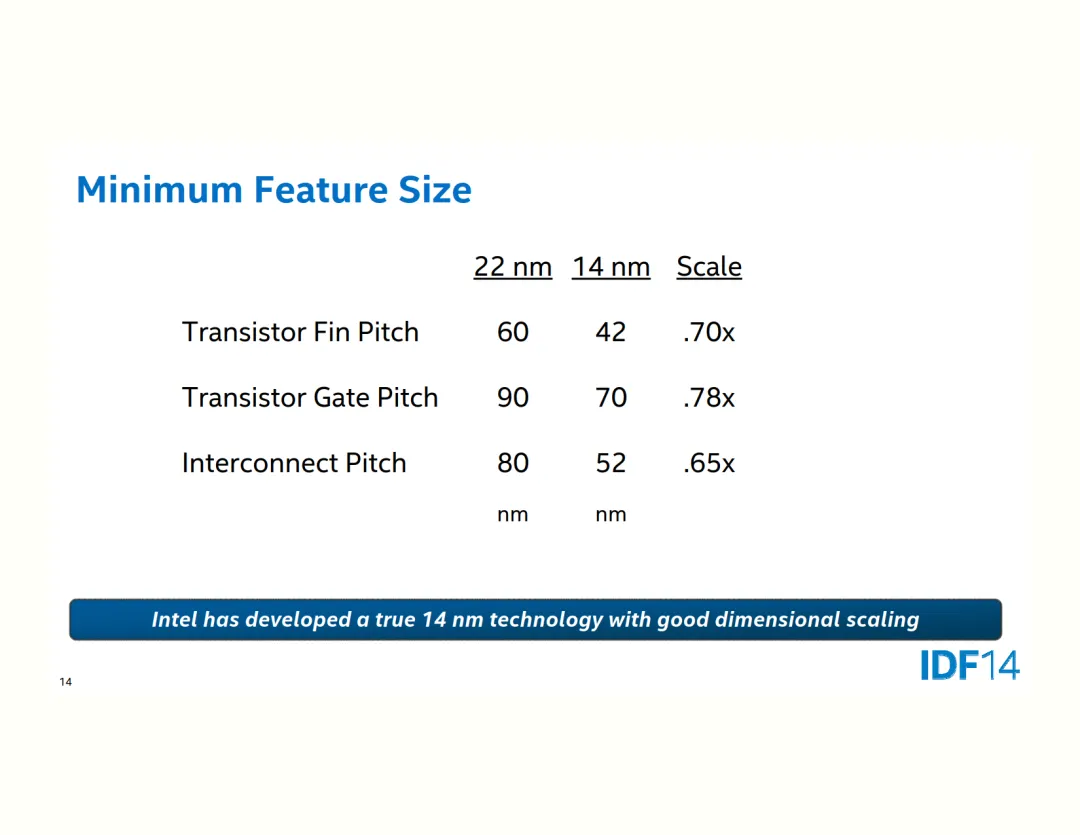

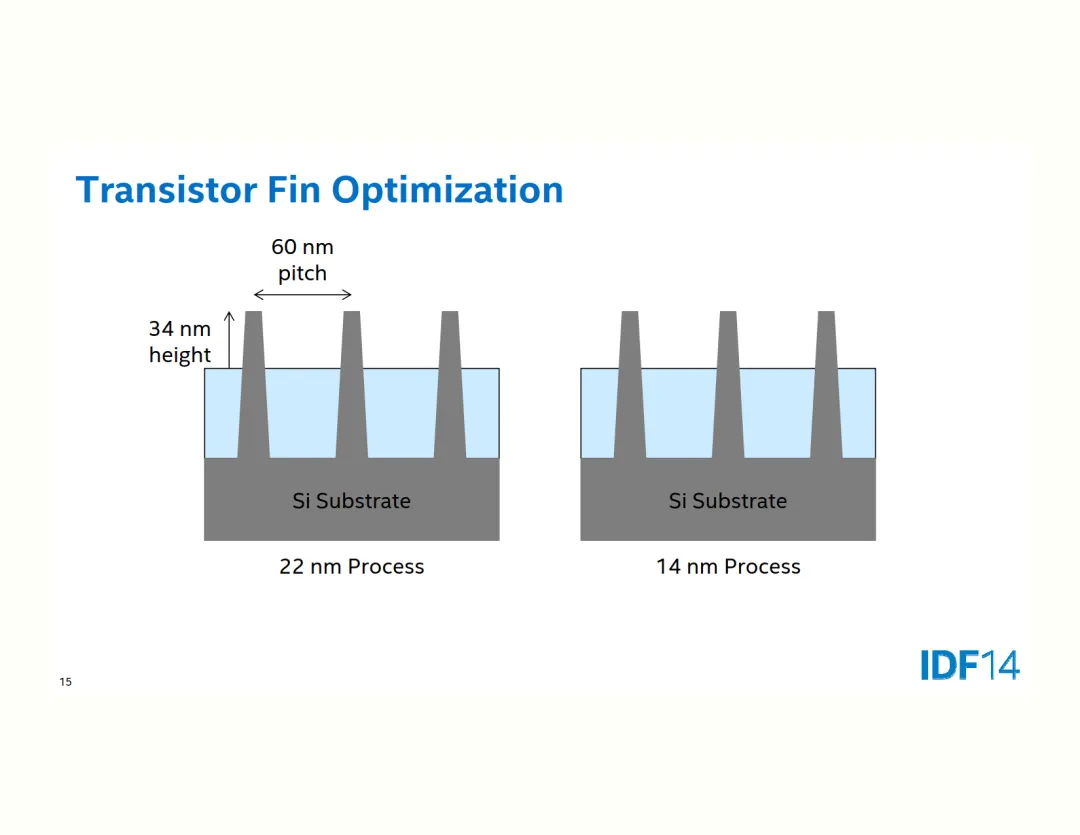

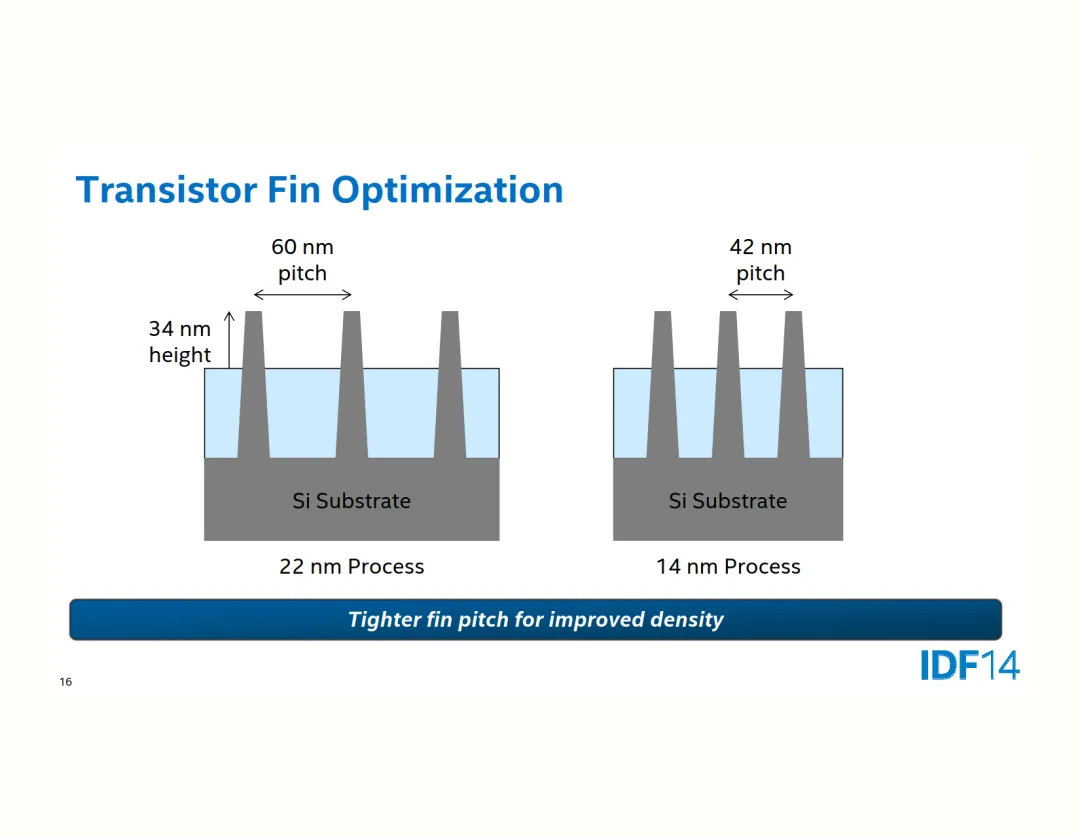

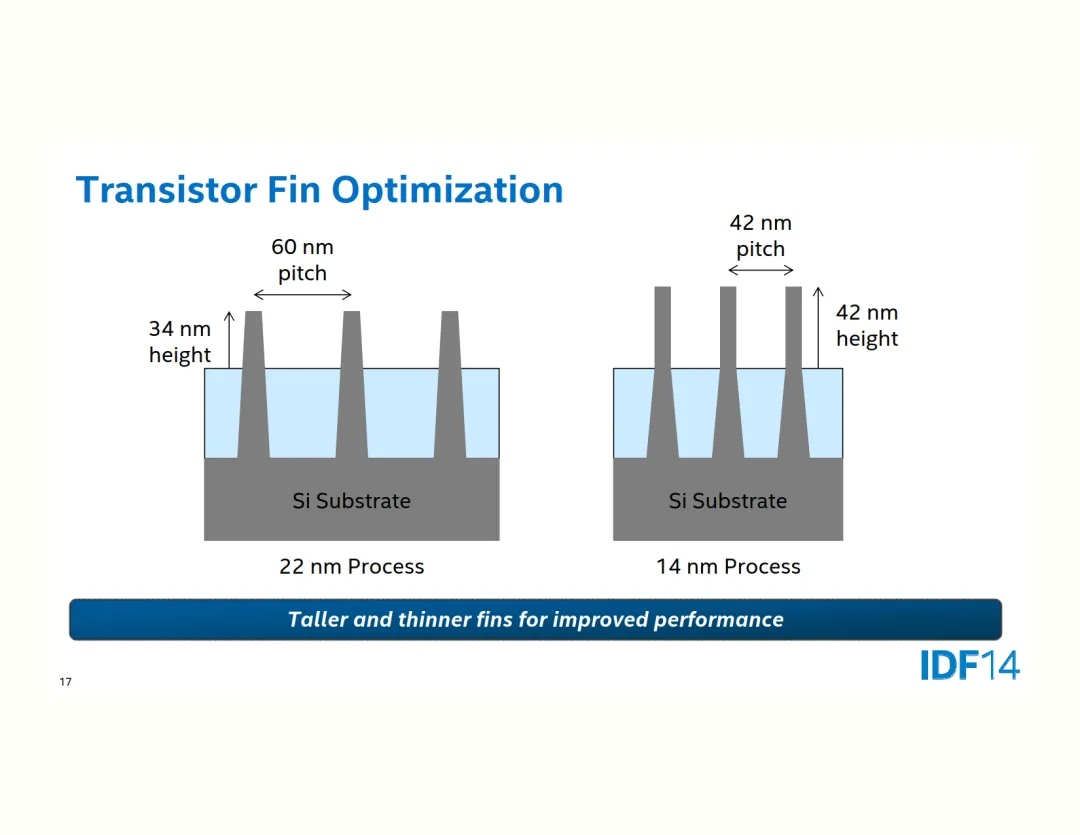

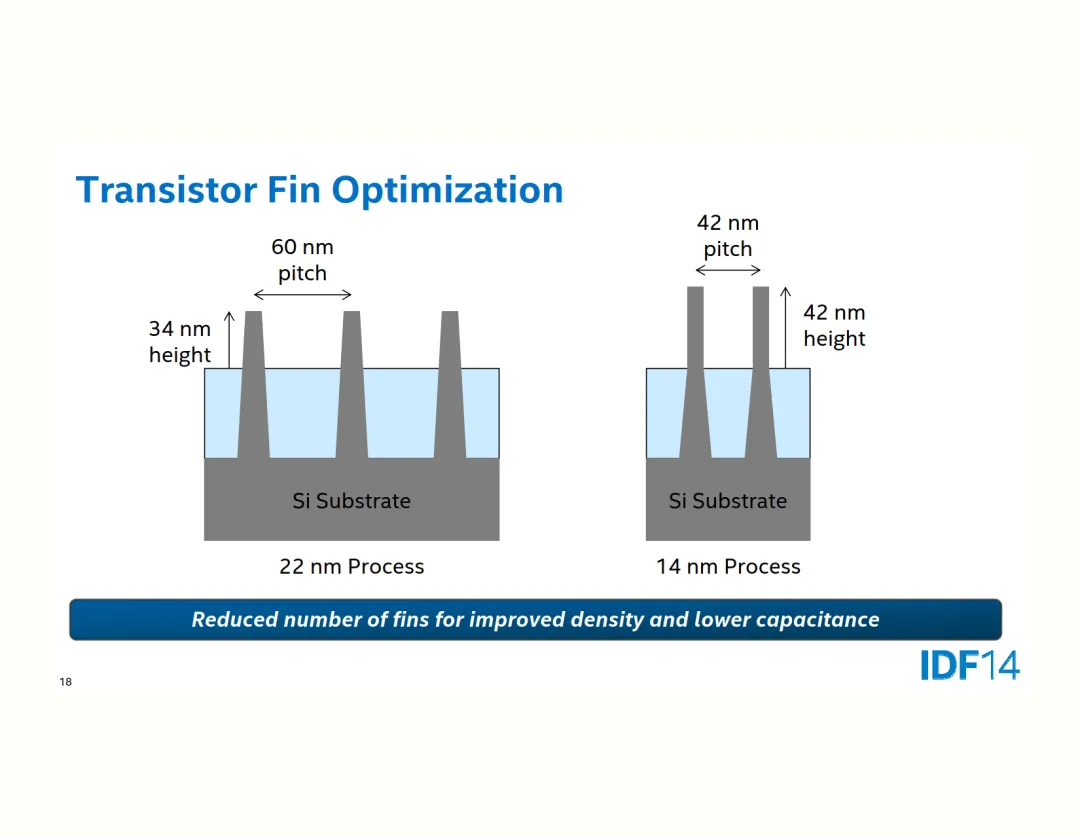

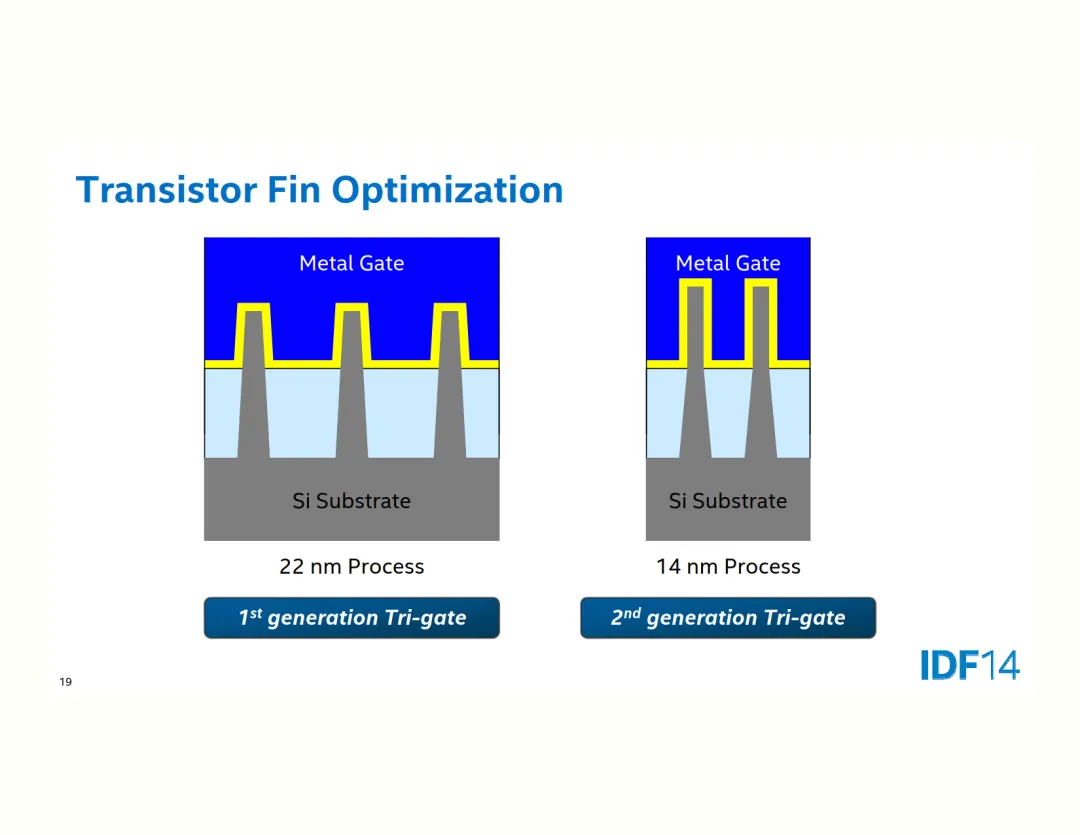

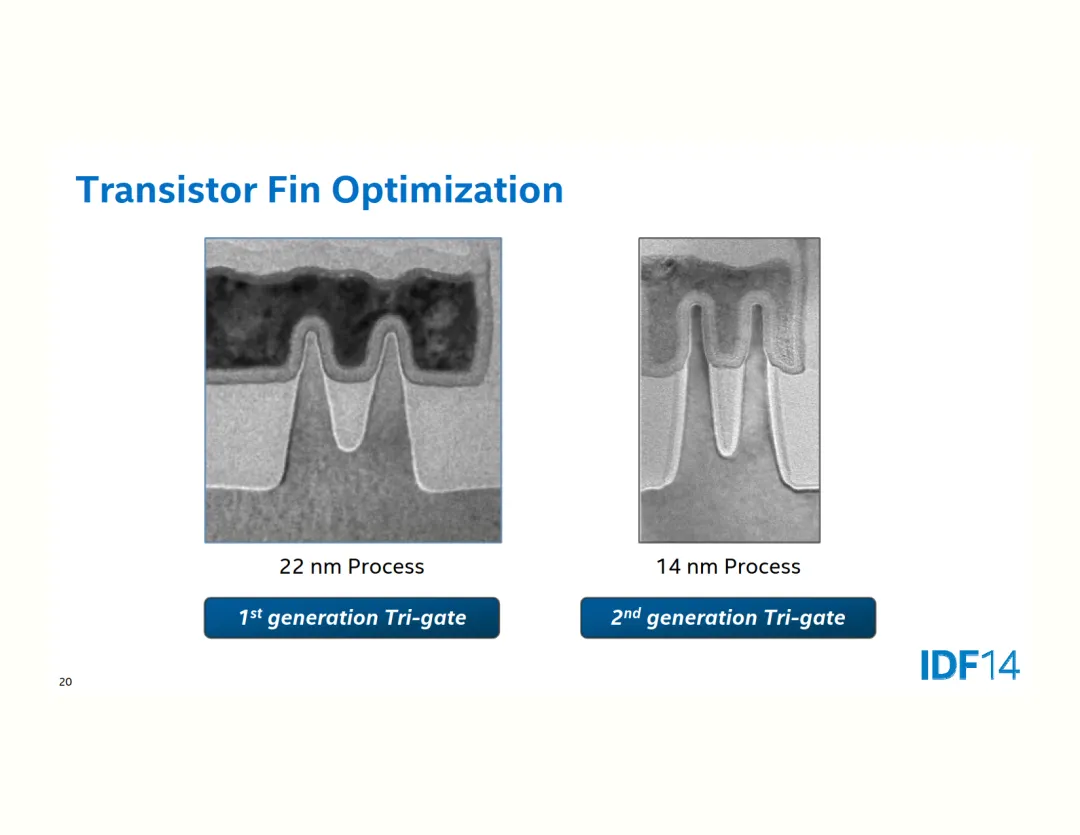

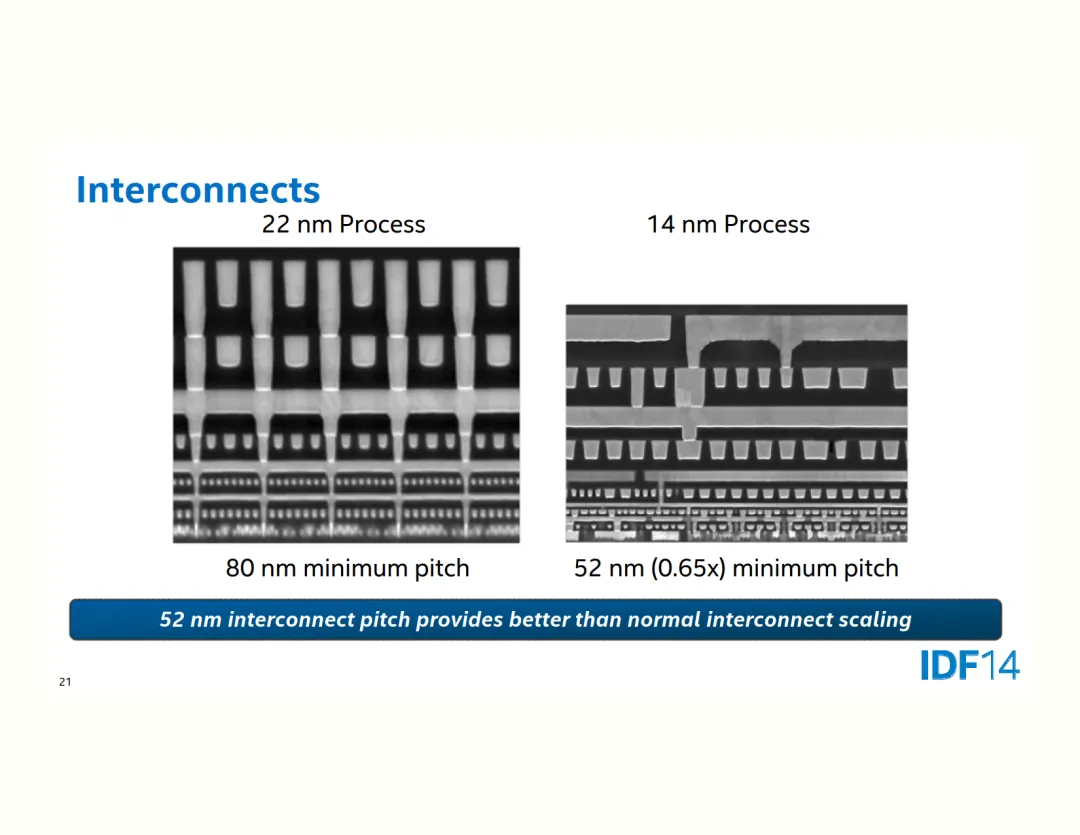

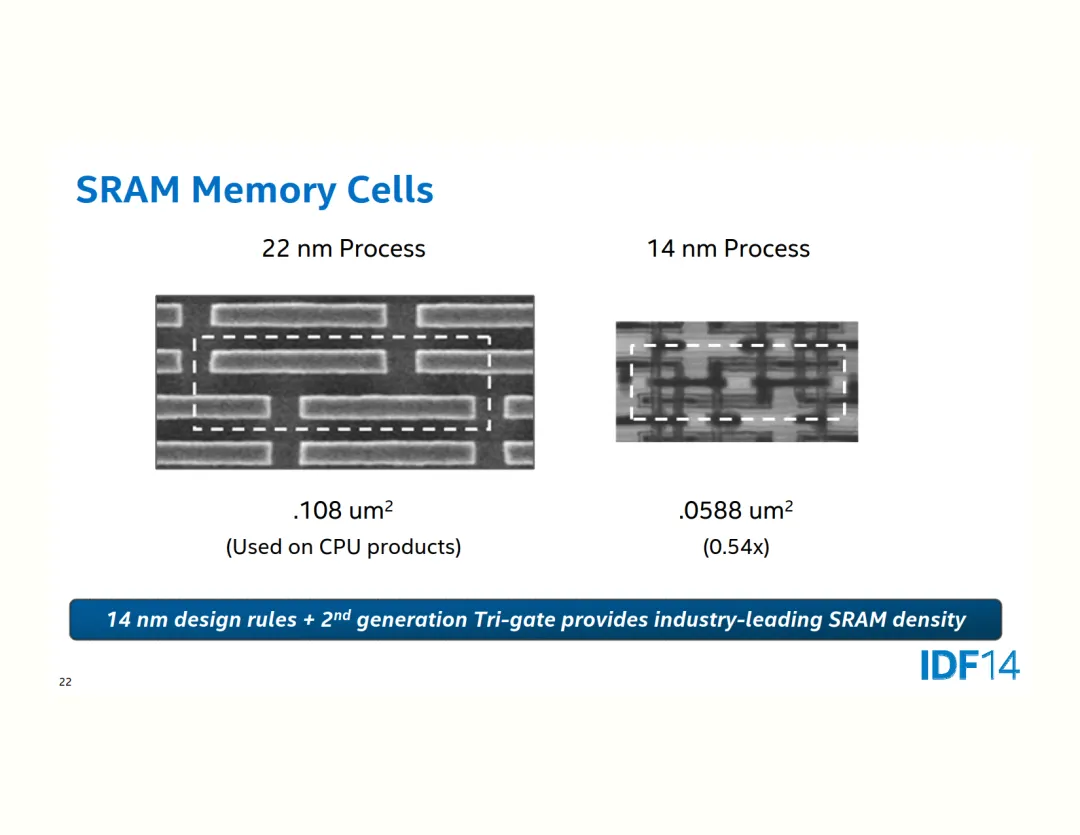

文档以“开启新视野”为主题,由英特尔资深院士Mark Bohr领衔讲解,核心围绕**第二代三栅极晶体管(FinFET)**展开,系统呈现14纳米工艺在逻辑面积缩放、单晶体管成本、产品优势及SoC功能菜单等维度的突破。彼时,英特尔已凭借22纳米三栅极晶体管出货超5亿颗芯片,而14纳米作为全球首个进入量产的技术,以42纳米鳍间距、70纳米栅极间距、52纳米互连间距的“真14纳米”维度缩放,实现了超越常规的密度提升——SRAM单元面积较22纳米缩小至0.0588μm²(0.54倍),逻辑面积每代缩放约0.53倍,且通过自对准双图案等先进工艺,让14纳米的密度比同期竞品“20/16/14纳米”技术高约1.3倍,甚至与竞品未来“10纳米”密度相当却早3年落地。

性能与功耗的平衡是14纳米的另一亮点:第二代三栅极晶体管优化了鳍的宽度(8nm)与高度,实现更高驱动电流与更低泄漏,支撑从服务器到移动始终在线电路的全场景产品需求;14纳米酷睿M处理器作为首款量产14纳米产品,集成13亿晶体管、82mm² die,以4.5W TDP实现无风扇设计,性能较前代提升超2倍(CPU快50%、图形快40%),电池续航翻倍,且达成“无冲突矿物”标准。成本层面,尽管晶圆因掩模步骤增加推高成本,但14纳米通过更优面积缩放维持了单晶体管成本的持续下降,延续摩尔定律的经济性优势。

文档还延伸至技术 roadmap,明确10纳米将进一步提升性能、功耗与成本表现,同时披露14纳米制造布局(俄勒冈、亚利桑那2014年投产,爱尔兰2015年跟进)及良率已进入健康区间,多款产品 ramp 可满足2015年上半年需求。后续补充的14+/14++增强版、与TSMC/Samsung等竞品的工艺对比,以及CMP工艺挑战等内容,进一步印证英特尔在14纳米节点已形成从晶体管到系统的全栈创新能力——不仅是技术的“更早更密”,更是性能的“领先20%以上”,为从高性能到低功耗的广泛产品提供了核心支撑。

简言之,这份文档不仅记录了英特尔14纳米工艺的量产里程碑,更诠释了其如何通过第二代三栅极晶体管、超缩放特征与深度设计-工艺协同,在摩尔定律趋近物理极限时,依然保持性能、密度、成本与功耗的行业领导力,为后续10纳米及更先进工艺奠定了坚实基础。